- 您现在的位置:买卖IC网 > Sheet目录1996 > HSP45106JC-33Z (Intersil)IC OSC NCO 33MHZ 84-PLCC

7

FN2809.8

October 16, 2008

they were RAMs, using the decoded address bus to select

one or the other.

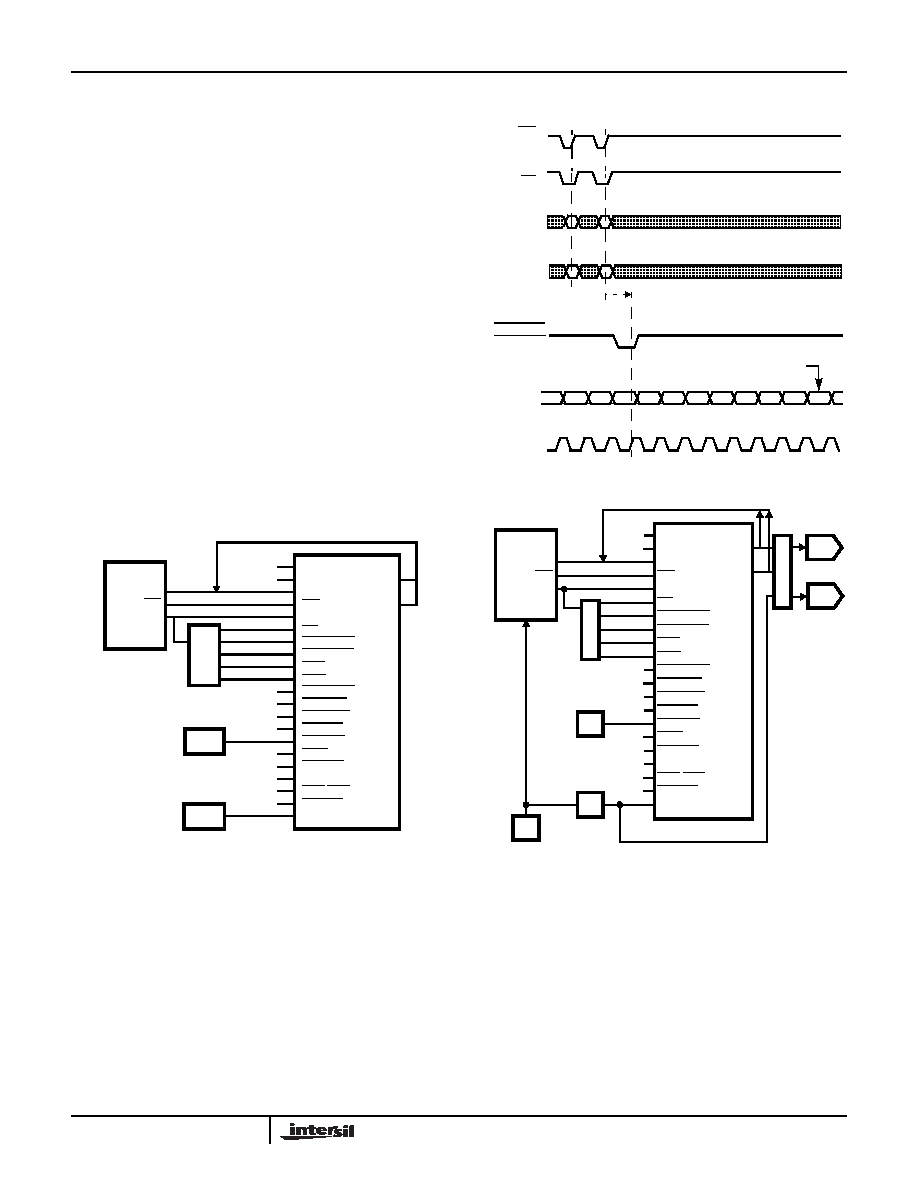

The timing for loading the Center Frequency Register (MSB

and LSB) and data being output on COS(15:0) and SIN(15:0)

is shown in Figure 3. This timing is independent of whether

the output data represents the phase accumulator data or the

SIN/COS Generator output.

When it is desired for the output of the NCO16 to be switched

back and forth between sine/cosine and the phase

accumulator, a circuit such as the one shown in Figure 4 could

be used. In this case, the sinusoidal output cannot be

interrupted, so the phase accumulator must be read out

between samples. This is possible due to the fact that the

TEST signal is simply the control line for a multiplexer on the

output of the SIN/COS Generator, but carries with it a

limitation on the maximum possible clock rate. Since TEST is

a synchronous input, the output of the NCO16 must be either

driven by the SIN/COS Generator or the phase accumulator

for an entire clock cycle. Therefore, the part must be driven at

twice the desired speed at all times so there is a clock cycle

available for TEST, when necessary. Note that the processor

must be driven from the same clock that generates the NCO

clock in order to maintain synchronous operation.

MOD0(2:0)

PMSEL

C(15:0)

WR

A(2:0)

CS

ENPOREG

ENCFREG

ENOFREG

ENPHAC

ENTIGEG

INHOFR

INITPAC

PACI

INITTAC

TEST

PAR/SER

BINFMT

CLK

SIN0-15

COS(15:0)

OES

OEC

HSP45106

DECODE

MICROPROCESSOR

DATA

WE

ADDRESS

GND

VCC

START

LOGIC

OSCILLATOR

FIGURE 2. CIRCUIT FOR READING PHASE ACCUMULATOR

OF NCO16

(15:0)

WR

A0-2

ENCFREG,

ENOFREG

COS0-15,

SIN0-15

TRANSFER DATA

TO CENTER OR OFFSET

FREQUENCY REGISTER

NEW

FREQUENCY

DATA

CS

FIGURE 3. NCO16 PIPELINE DELAY

CLK

WRITE

REGISTER

WRITE

LS INPUT

REGISTER

MS INPUT

C0-15

MOD0-2

PMSEL

C0-15

WR

A0-2

CS

ENPOREG

ENCFREG

ENOFREG

ENPHAC

ENTIGEG

INHOFR

INITPAC

PACI

INITTAC

TEST

PAR/SER

BINFMT

CLK

SIN0-15

COS0-15

OES

OEC

HSP45106

DECODE

MICROPROCESSOR

DATA

WE

ADDRESS

GND

VCC

OSCILLATOR

÷2

REGISTER

DAC

>

FIGURE 4. CIRCUIT FOR READING PHASE ACCUMULATOR

OF NCO16 WHILE GENERATING SINUSOID

START

LOGIC

HSP45106

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HSP45116AVC-52Z

IC OSC NCO 52MHZ 160-MQFP

ICL7109EPL+

IC ADC 12BIT 3-ST 40-DIP

ICM7217AIPI

IC OSC UP/DWN CNTR 2MHZ 28-DIP

ICM7217CIPI

IC OSC UP/DWN CNTR 2MHZ 28-DIP

ICM7242IPA

IC OSC BINARY CTC 13MHZ 8-DIP

ICM7250IWE+T

IC OSC BINARY CTC 15MHZ 16SOIC

ICM7556IPD

IC OSC TIMER DUAL 500KHZ 14-DIP

ICM7556MJD

IC OSC TIMER DUAL 1MHZ 14DIP

相关代理商/技术参数

HSP45106JI-25

制造商:Rochester Electronics LLC 功能描述:- Bulk

HSP45116

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator

HSP45116 WAF

制造商:Intersil Corporation 功能描述:

HSP45116/883

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator

HSP45116_04

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator

HSP45116883

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator

HSP45116A

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator

HSP45116A_07

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator